北海道千歳市に建設中のラピダスの工場。2025年1月28日撮影(資料写真、写真:アフロ)

北海道千歳市に建設中のラピダスの工場。2025年1月28日撮影(資料写真、写真:アフロ)

(湯之上 隆:技術経営コンサルタント、微細加工研究所所長)

前工程だけでなく後工程にも参入するラピダス

半導体実装および後工程技術の国際学会「ICEP-IAAC2025」が2025年4月に長野県で開催され、その基調講演でラピダスが発表を行ったという(日経クロステック、『ラピダス、インテルが実装戦略披露、光電融合のOSATに名乗り』、2025年6月19日)。

そのラピダスの講演の内容を上記記事は次のように報じている。

<半導体ファウンドリのラピダスが、最先端のパッケージング技術の開発を急ピッチで進めている。急成長する生成AI(人工知能)市場で、GAFAMなどの大手顧客からの受注を獲得していくためだ。ハイブリッド結合やパネルレベルパッケージなどの設計・製造・検査に関する次世代技術をいち早く確立し、パッケージングまで含んで、どこよりも速い短TAT(Turn Around Time)製造を目指す。>(原文ママ)

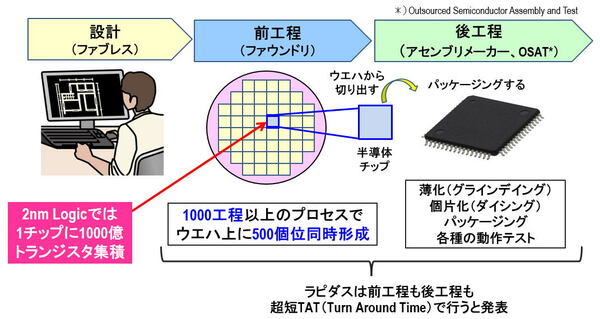

半導体は、設計、ウエハ上にチップをつくり込む前工程、そのチップを切り出してパッケージングする後工程の3段階で製造される(図1)。

2022年11月にラピダスは、「2027年までに先端の2nmのロジック半導体を量産する」と発表して大きな注目を集めた。その後、ラピダスは、今年(2025年)4月に北海道千歳市の工場にパイロットライン(試作ラインのようなもの)を構築し、ウエハを流し始めた。

しかし筆者は、ラピダスが前工程で2nmのロジック半導体を量産できるとは思っていない。さらに、ラピダスが後工程の分野で、GAFAM(グーグル、アマゾン、メタ=旧フェイスブック、アップル、マイクロソフト)用のAI半導体用のパッケージを短TATで行うことも不可能だと考えている。

そこで本稿では、ラピダスがAI半導体用パッケージを短TATでつくることが困難な根拠を示したい。その前に、現在の半導体産業では、後工程のパッケージが、前工程以上に注目を集めていることを説明する。