1996年から15年間続いたコンソーシアム、半導体先端テクノロジーズ(通称「セリート」)と、セリートを中心とした国家プロジェクト「あすか」が、2011年3月に終了した(4月26日の記事「まるで日本半導体を見るようだ、政府の「対策本部」乱立は機能しない」に詳細を記述した)。

その後、つくばのクリーンルームをどうするのだろうと思っていたら、経済産業省の支援の下、EUVL基盤開発センター(EUVL Infrastructure Development Center, Inc:以下「EIDEC」)という会社ができていた。代表取締役社長は、セリートから横滑りで渡辺久恒氏が就任している。

EIDECには、東芝およびルネサス エレクトロニクスの他に、4社のフォトマスクメーカーと5社のレジストメーカーが参加している。また、海外からインテル、サムスン電子、TSMC、ハイニックス、サンデイスクが共同開発者として加わっている。その他、製造装置メーカーとして東京エレクトロンが参加する。

次世代の微細加工技術を追求するコンソーシアム

EIDECの目的は、線幅16ナノミリ以降の次世代(16ナノ~11ナノミリ世代)微細加工装置EUVLのフォトマスク技術およびレジスト技術の開発にある。

EUVLとは、「Extreme Ultra Violet Lithograph」、すなわち極端紫外光(EUV)を用いたリソグラフィ技術のことである。

フォトマスクとは回路の原版である。この原版をもとに、シリコンウエハに回路パターンを転写する。レジストとは感光性樹脂であり、シリコンウエハ上に塗布した後、フォトマスクを介して、EUVを照射して回路パターンを形成する。

日本のフォトマスクメーカーおよびレジストメーカーの競争力は非常に高い。したがって、EIDECは、このような材料メーカーにとっては有効なコンソーシアムであると思われる。また、東芝だけでなく、インテル(米国)、サムスン(韓国)、TSMC(台湾)など海外のトップメーカーが加わることも、これまでにないオープンな形態であり、期待が持てる。

しかし、首を傾げざるを得ない点もある。まず、現在、唯一EUVL装置を開発しているオランダのASMLが加わっていない。パターン形成のためには、「フォトマスク製造→レジスト塗布→露光→現像」という過程が必要だ。塗布と現像は、東京エレクトロンのコータ/デベロッパを使うと予想されるが、ASMLの露光機がない。

次に、EUVLの国際的コンソーシアムとしては、既に欧州のIMECと米国ニューヨーク州オルバニーを拠点とするSEMATECHが5年以上前から活動を行っている。この2拠点には、当然、ASMLの露光機が入っている。この2つのコンソーシアムに対して、後発のEIDECの研究開発は、どんな意味を持つのだろうか?

さらに、EIDEC始動の直前に、ルネサス エレクトロニクスが参加を表明した。しかし、ルネサスは次世代の微細加工からは手を引き、TSMCなどのファンドリーに委託すると発表したはずだ。方針を変えたのだろうか。だが、ルネサスの体力を考えると、1台100億円もする露光装置を買えるとはとても思えない。それとも、あくまで微細化にこだわりたいのだろうか。

ルネサスがEIDECに加わって、16ナノミリ以降の微細化技術を開発する意味はないと思うが、半導体産業が40年以上に渡ってひたすら微細化を追求してきたのはなぜなのか?

また、巨額の投資が必要であり、1社では開発が難しくなっても、なお東芝、インテル、サムスン、TSMCなどが微細化をやめない理由は何か? 微細化の行きつく先には何があるのか?

微細化で半導体の高性能化と低コスト化が実現

「トランジスタの集積度は18~24カ月で2倍になる」。これが、有名なムーアの法則である。トランジスタとは、集積回路を形成する基本素子である。

ところが、集積度を増大させる際に、トランジスタなど素子の大きさが一定のままであったら、チップサイズも巨大化していく。半導体の特徴は、圧倒的に小さな領域に電子回路を形成できることにある。したがって、チップサイズを巨大化することなく、集積度を増大させるためには、素子を微細化する必要がある。

そのため、半導体の集積度が4年で3倍の速度で増大するとともに、トランジスタなどの素子の大きさは4年で0.7倍の速度で微細化され続けてきた。1970年以降、40年以上が経過して、トランジスタの集積度は10億個以上になり、トランジスタの大きさは数百分の1以下に微細化された。

しかし、微細化は、単に集積化のためだけに行われたのではない。微細化の背景には、「スケーリング則」という指導原理が存在した。

このスケーリング則は、1974年にIBMのロバート・デナードらが発表した。スケーリング則に従って微細化を行えば、集積度が向上するのはもちろんのこと、トランジスタの動作速度が向上し、消費電力が低下する。

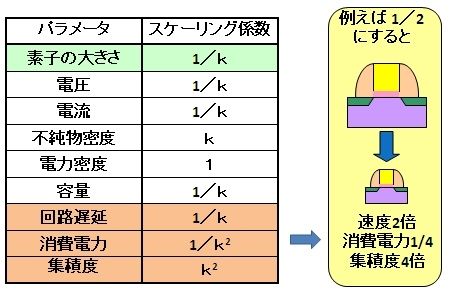

例えば、あるトランジスタの縦、横、高さをそれぞれ2分の1にし、電圧を2分の1にすれば、トランジスタの動作速度は2倍になり、消費電力は4分の1になり、集積度は4倍になる(下の図)。

74年に発表されたスケーリング則。微細化によってトランジスタの動作速度が向上し、消費電力が低下することを示す。

74年に発表されたスケーリング則。微細化によってトランジスタの動作速度が向上し、消費電力が低下することを示す。